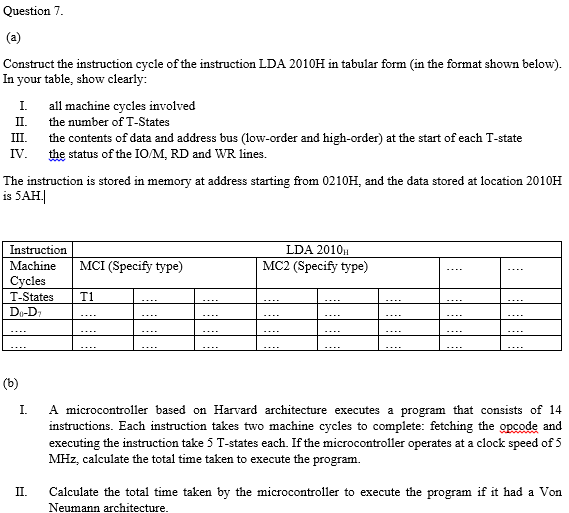

Machine Cycle For Lda Instruction

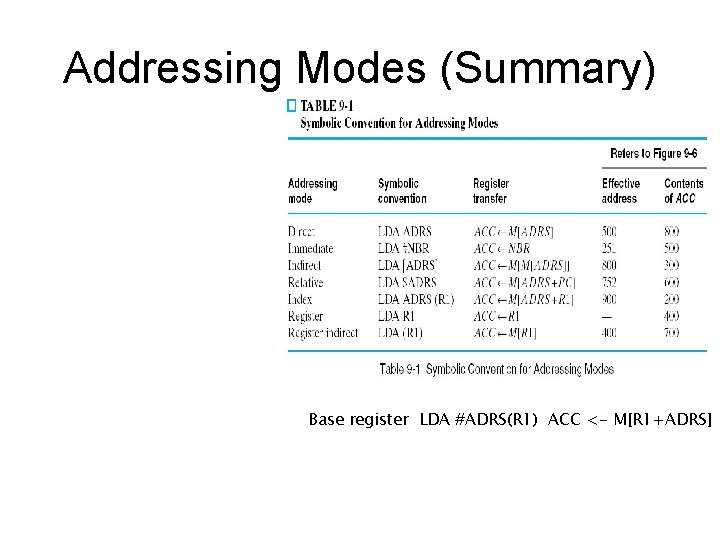

A program residing in the memory unit of a computer consists of a sequence of instructions. LDA 2 or A Load AC from M STA 3 or B Store AC in M BUN 4 or C Branch unconditionally to m BSA 5 or D Save return address in m and branch to m1.

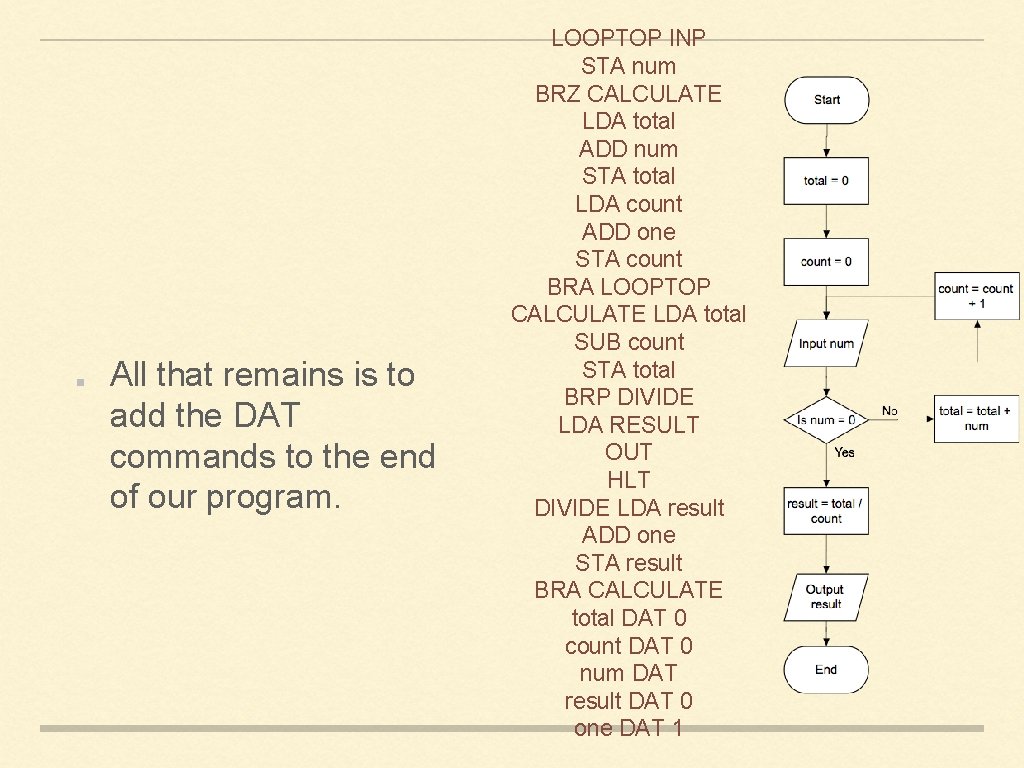

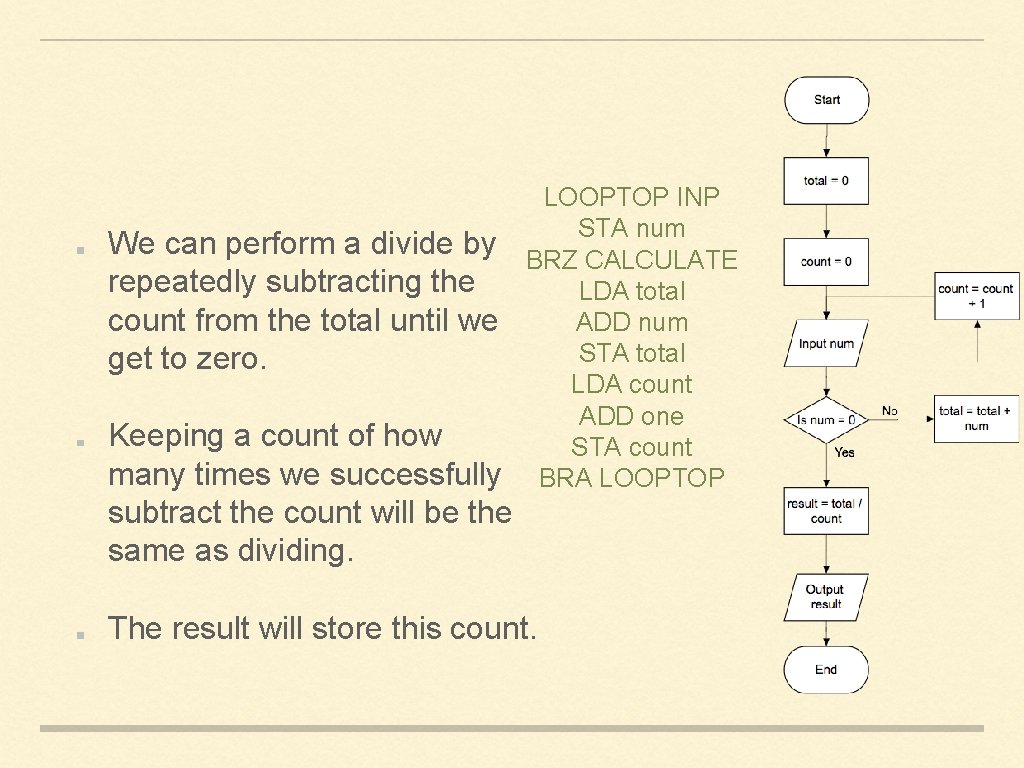

The Little Man Computer What Is The Little

Here is the timing diagram of the instruction LDA 4050H Summary So this instruction LDA 4050H requires 3-Bytes 4-Machine Cycles Opcode Fetch Memory Read Memory Read Memory Read and 13 T-States for execution as shown in the timing diagram.

Machine cycle for lda instruction. A line with slope indicates change in the data and dotted line indicates high impedance state. 16 bit address. The instruction cycle is the process executed by the computer CPU to execute one single program instruction.

We assumed a new 2-bit register called Instruction Cycle Code ICCThe ICC designates the state of processor in terms of which portion of the cycle it is in-. Fetch instruction from memory. In this machine cycle processor places the address of next incremented memory location and gets the low-order byte.

During one machine cycle the processor executes at least two steps fetch data and execute command. The diagram shows how various elements work coordinating with each other to process the instructions. Summary So this instruction LDAX B requires 1-Byte 2-Machine Cycles Opcode Fetch Memory Read and 7 T-States for execution as shown in the timing diagram.

The Opcode is stored in memory. In 1st Machine cycles the 8085 microprocessor places the address of memory loaction on the address bus and fetches the opcode of LHLD instruction. The machine cycle is the part of instruction cycle.

The Indirect Cycle is always followed by the Execute CycleThe Interrupt Cycle is always followed by the Fetch CycleFor both fetch and execute cycles the next cycle depends on the state of the system. Here is the timing diagram of LDAX B instruction execution. Here ten clock cycles are needed for the OF decode and performing the execution.

In order to fetch the Opcode from memory processor executes the Opcode Fetch machine cycle. Memory read machine cycle is a machine cycle during which memory is read. Reading data from the zeropage typically needs one cycle less as reading from an absolute address.

These instructions are executed by the processor by going through a cycle for each instruction. The second machine cycle is read. Each instruction of the microprocessor has one byte Opcode.

The more complex a command is more data to fetch the more cycles it will take to execute. In a basic computer each instruction cycle consists of the following phases. The time taken by the microprocessor to execute the Opcode Fetch cycle is 4T T- states.

For example the instruction LDA 8900H which is a 3-byte instruction has three memory read cycles immediately after the opcode fetch cycle. Load accumulator direct. The Processor starts the instruction cycle by fetching the instruction decoding the instruction then performing the desired operation and finally storing the result in the memory.

The third machine cycle is also read. Summary So this instruction SDA 4050H requires 3-Bytes 4-Machine Cycles Opcode Fetch Memory Read Memory Read Memory Write and 13. Suppose at location C002H we have 36H which is the opcode for the instruction MVI M ABH.

Using machine instruction set - Usually when the operation is not included in the instruction set - Hardware Implementation - Implementation of an operation in a computer. Instruction cycle is divided into 1 to 5 machine cycles depending on instruction Each machine cycle is divided into 3 to 5 states Each state lasts one clock cycle Processor performs one or more parallel micro-ops per state determined by control signals Machine cycles are. So every instruction starts with Opcode Fetch machine OFM cycle.

The first four cycles of the clock constitute the OF machine cycle and the next three cycles of the clock will be Memory Read machine cycle and the last three clock cycles will be Memory Write machine cycle. 56 rows LDA. In machine cycle various operations like opcode fetch memory read memory write IO read IO write are performed.

Microprocessor Lecture 16 Instruction Set Of 8085 Lda 16 Bit Address By Er Pawan Chandani Youtube

Lda Instruction Cycle Of 8085 Microprocessor Youtube

Lombardini Lda 96 97 100 820 Diesel Engine Parts Manual Diesel Engine Diesel Engineering

Question 7 Construct The Instruction Cycle Of The Chegg Com

Table 2 From Big Data Software Engineering Analysis Of Knowledge Domains And Skill Sets Using Lda Base Computer Science Engineering Software Engineer Big Data

Discarded With The Mpp Instruction But The Two Center Instructions Use Mrd To Copy The Right Value To The Top Of The Ladder Logic Plc Programming Instruction

Gpu Implementation Of Ga Lda A Input Tensors Are Generated For All Download Scientific Diagram

The Little Man Computer What Is The Little

Question 7 Construct The Instruction Cycle Of The Chegg Com

Multi Class Lda And Svm Classification Accuracy Results Download Table

Education For All Sap 1 Instructions And Instruction Cycle

Rohan Ranjangaonkar How To Find T States Of 8085 Microprocessor

Timing Diagram Of Sta In Instructions Of 8085 Free 8085 Microprocessor Lecture

Performance Time Taken By The System To Execute

Timing Diagram Of Lda 16 Bit Address Youtube

Timing Diagrams And Machine Cycles Learn With 8085 Instructions

07 Lda 16 Bit Address Instruction In 8085 Microprocessor Data Transfer Group Gate Exam Youtube

Note Ioe Microprocessor System

Post a Comment for "Machine Cycle For Lda Instruction"